Project information

- Affiliation: BITS, Pilani

- Project Title: Fault-Tolerant Routing Algorithm for Mesh based NoC using Reinforcement Learning

About the Project

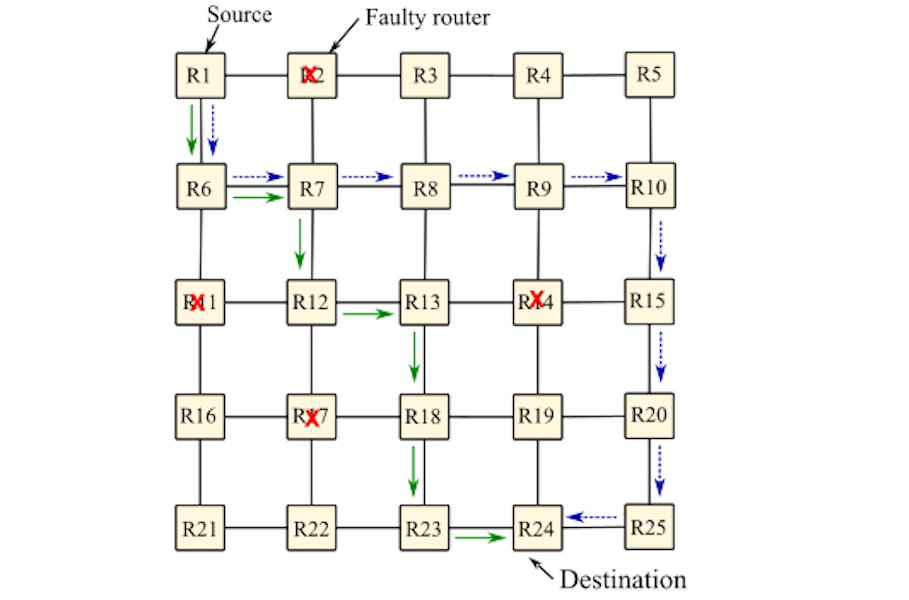

Network-on-Chip (NoC) is an efficient and scalable on-chip interconnection framework, designed to address communication challenges in multiprocessor system-on-chips (MPSoCs) based architectures. The major backbone of the communication infrastructure of NoC are links and routers. In the nano-scale era, NoCs are susceptible to faults that may degrade the system performance at a higher level. In NoC, faults can occur at any abstract level of the communication infrastructure. Hence, there is a need for fault-tolerant strategies that address reliability while improving system performance. In this work, we designed a fault-tolerant routing algorithm to address link and router faults in the mesh-based NoC design. Unlike traditional approaches, we employed a reinforcement learning (RL) based fault-tolerant routing algorithm to address the link and router faults in NoC.

Publication:

Fault-Tolerant Routing Algorithm for Mesh based NoC using Reinforcement Learning (link)

Jagadheesh Samala, Harshvardhan Takawale, Yash Chokhani, P Veda Bhanu, J Soumya

24th International Symposium on VLSI Design and Test (VDAT), July. 2020